|

| |||

|---|---|---|---|

|

|

||

VERIFICATION PLAN

Overview

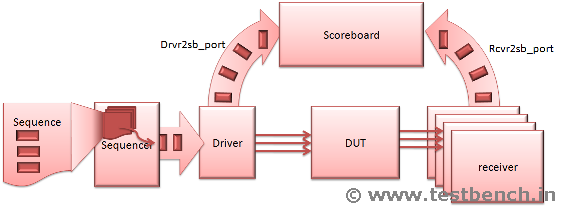

This Document describes the Verification Plan for Switch. The Verification Plan is based on System Verilog Hardware Verification Language. The methodology used for Verification is Constraint random coverage driven verification.

Feature Extraction

This section contains list of all the features to be verified.

1)

ID: Configuration

Description: Configure all the 4 port address with unique values.

2)

ID: Packet DA

Description: DA field of packet should be any of the port address. All the 4 port address should be used.

3)

ID : Packet payload

Description: Length can be from 1 to 255. Send packets with all the lengths.

4)

ID: Length

Description:

Length field contains length of the payload.

5)

ID: FCS

Description:

Good FCS: Send packet with good FCS.

Bad FCS: Send packet with corrupted FCS.

Stimulus Generation Plan

1) Packet DA: Generate packet DA with the configured address.

2) Payload length: generate payload length ranging from 2 to 255.

3) Generate good and bad FCS.

Verification Environment

Overview

This Document describes the Verification Plan for Switch. The Verification Plan is based on System Verilog Hardware Verification Language. The methodology used for Verification is Constraint random coverage driven verification.

Feature Extraction

This section contains list of all the features to be verified.

1)

ID: Configuration

Description: Configure all the 4 port address with unique values.

2)

ID: Packet DA

Description: DA field of packet should be any of the port address. All the 4 port address should be used.

3)

ID : Packet payload

Description: Length can be from 1 to 255. Send packets with all the lengths.

4)

ID: Length

Description:

Length field contains length of the payload.

5)

ID: FCS

Description:

Good FCS: Send packet with good FCS.

Bad FCS: Send packet with corrupted FCS.

Stimulus Generation Plan

1) Packet DA: Generate packet DA with the configured address.

2) Payload length: generate payload length ranging from 2 to 255.

3) Generate good and bad FCS.

Verification Environment

Index

Introduction

Specification

Verification Plan

Phase 1 Top

Phase 2 Configuration

Phase 3 Environment N Testcase

Phase 4 Packet

Phase 5 Sequencer N Sequence

Phase 6 Driver

Phase 7 Receiver

Phase 8 Scoreboard

Report a Bug or Comment on This section - Your input is what keeps Testbench.in improving with time!

Introduction

Specification

Verification Plan

Phase 1 Top

Phase 2 Configuration

Phase 3 Environment N Testcase

Phase 4 Packet

Phase 5 Sequencer N Sequence

Phase 6 Driver

Phase 7 Receiver

Phase 8 Scoreboard

Report a Bug or Comment on This section - Your input is what keeps Testbench.in improving with time!